Исследование дешифраторов

Цель работы

1. Ознакомление с принципом работы дешифраторов.

2. Исследование влияния управляющих сигналов на работу дешифраторов.

3. Реализация и исследование функциональных модулей на основе дешифраторов.

Краткие сведения из теории

1. Комбинационные схемы. Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Для реализации комбинационных схем используются логические элементы, выпускаемые в виде интегральных схем. В этот класс входят интегральные схемы дешифраторов, шифраторов, мультиплексоров, демультиплексоров, сумматоров.

В этой главе для удобства вместо схемы дешифратора используется схема демультиплексора, это возможно благодаря сходству алгоритмов работы.

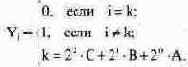

2. Дешифраторы. Дешифратор - логическая комбинационная схема, которая имеет п информационных входов и 2n выходов. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2n выходов. Обычно п равно 2,3 или 4. На рис. 13.1 изображен дешифратор' с п = 3, активным уровнем является уровень логического нуля. На входы С, В, А можно подать следующие комбинации логических уровней: 000, 001, 010...Ill, всего 8 комбинаций. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал, на остальных - высокий. Номер этого единственного выхода, на котором формируется активный (нулевой) уровень, соответствует числу N, определяемому состоянием входов С, В, А следующим образом: N = С22 + В2' + А'2°. Например, если на входы подана комбинация логических уровней 011, то из восьми выходов микросхемы (YO, Y1...Y7) на выходе с номером N=3 установится нулевой уровень сигнала (Y3=0), a все остальные выходы будут иметь уровень логической единицы. Этот принцип формирования выходного сигнала можно описать следующим образом:

Видно, что уровень сигнала на выходе Y3 описывается выражением:

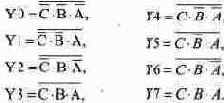

В таком же виде можно записать выражения для каждого выхода дешифратора:

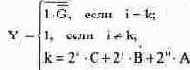

Помимо информационных входов А,В,С дешифраторы обычно имеют дополнительные входы управления G. Сигналы на этих входах, например, разрешают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов. Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом — уровень логического нуля. На рис. 13.1 представлен дешифратор с одним инверсным входом управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

У дешифратора с несколькими входами управления функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора 74138 с одним прямым входом управления G1 и двумя инверсными G2A и G2B (рис. 13.2) функции выхода Yi и разрешения G имеют вид:

Обычно входы управления используются для каскадирования (увеличения разрядности) дешифраторов или при параллельной работе нескольких схем на общие выходные линии.

3. Использование дешифратора в качестве демультиплексора. Дешифратор может быть использован и как демультиплексор - логический коммутатор, подключающий входной сигнал к одному из выходов. В этом случае функцию информационного входа выполняет один из входов разрешения, а состояние входов С, В и А задает номер выхода, на который передается сигнал со входа разрешения. Порядок проведения экспериментов

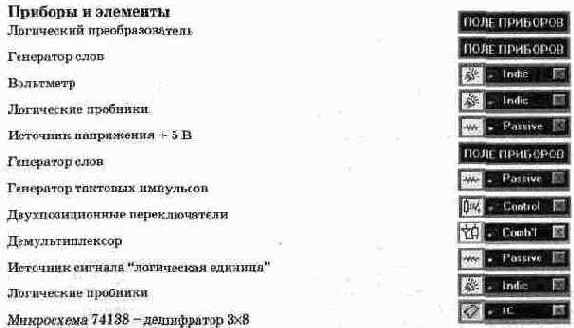

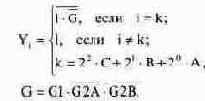

Эксперимент 1. Исследование принципа работы дешифратора 3х8 в основном режиме. Откройте файл с13_01 со схемой, изображенной на рис. 13.3. Включите схему. Подайте на вход G уровень логической единицы. Для этого клавишей G ключ G установить в верхнее положение. Определите и запишите уровни сигналов на выходах YO...Y7 в таблицу истинности при G = 1 (табл. 13.1 в разделе "Результаты экспериментов"). Подайте на вход G уровень логического нуля (ключ G установите в нижнее положение). Убедитесь, что дешифратор перешел в рабочий режим и на одном из выходов установился уровень логического нуля. Подавая все возможные комбинации уровней логических сигналов на входы А, В, С с помощью одноименных ключей и определяя с помощью логических пробников уровни логических сигналов на выходе схемы, заполните таблицу истинности дешифратора при G=0 (табл. 13.1. в разделе "Результаты экспериментов").

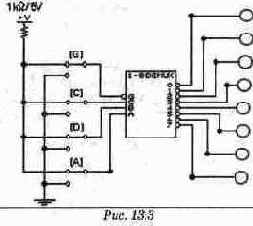

Эксперимент 2. Исследование принципа работы дешифратора 3х8 в режиме 2х4. а). В схеме рис. 13.3 подключите вход С к общему проводу (земле), задав С=0 (рис. 13.4). Изменяя уровни сигналов на входах В и А и наблюдая уровни сигналов на выходах схемы, с помощью пробников заполните таблицу истинности дешифратора (табл. 13.2 в разделе "Результаты экспериментов"). Укажите выходы, на которых уровень сигнала не меняется. б). Проделайте пункт а) при С=1, для чего вход С подключите к источнику логической единицы. Заполните таблицу истинности дешифратора (табл. 13.3 в разделе "Результаты экспериментов"). в). Проделайте пункт а), заземлив вход В (В=0), а на входы А и С подавая все возможные комбинации логических уровней. Заполните таблицу истинности (табл. 13.4 в разделе "Результаты экспериментов"), там же укажите номера выходов, на которых уровень логического сигнала не изменяется.

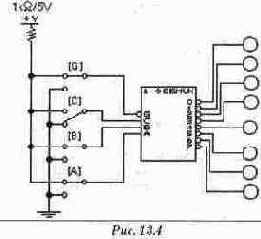

Эксперимент 3. Исследование работы дешифратора в качестве демультиплексора. Откройте файл с13_02 со схемой, изображенной на рис. 13.5. Включите схему. В пошаговом режиме работы генератора слов подайте на входы С, В, А демультиплексора слова, эквивалентные числам от 0 до 7. Наблюдая при помощи логических пробников уровни сигналов на выходах, заполните таблицу функционирования (табл. 13.5 в разделе "Результаты экспериментов"). Убедитесь, что изменяющийся сигнал на входе G поочередно появляется на выходах дешифратора.

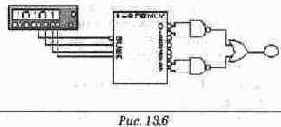

Эксперимент 4. Исследование дешифратора 3х8 с логической схемой на выходе. Откройте файл с13_03 со схемой, изображенной на рис. 13.6. Включите схему. Установите генератор слов в пошаговый режим. Последовательно подавая слова от генератора на вход схемы и наблюдая уровень логического сигнала на выходе схемы с помощью логического пробника, составьте таблицу истинности функции F, реализуемой схемой на выходе (табл. 13.6 в разделе "Результаты экспериментов"). По таблице запишите аналитическое выражение функции и занесите полученное выражение в раздел "Результаты экспериментов".

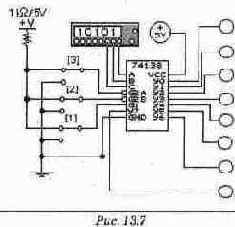

Эксперимент 5. Исследование микросхемы 74138. а). Откройте файл с13_04 (рис. 13.7). Установите генератор слов в пошаговый режим. Включите схему. С помощью соответствующих ключей установите состояние управляющих входов G1=0, G2A=G2B=1. Подавая на входы А, В, С слова от генератора слов и наблюдая состояние выходов с помощью логических пробников, заполните таблицу функционирования дешифратора 74138 (табл. 13.7 в разделе "Результаты экспериментов"). б). Повторите операции пункта а) при G1=G2A=1, G2B=0. Заполните таблицу функционирования дешифратора 74138 (табл. 13.8 в разделе "Результаты экспериментов").

в). Повторите операции пункта а) при G1=1, G2A=G2B=0. Заполните таблицу функционирования дешифратора 74138 (табл. 13.9 в разделе "Результаты экспериментов").

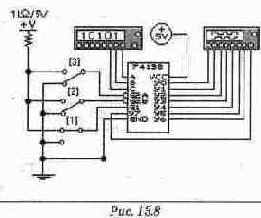

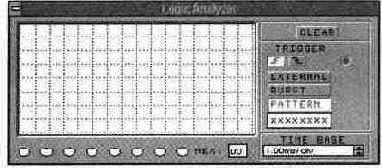

Эксперимент 6. Исследование микросхемы 74138 с помощью логического анализатора. Откроите файл с13_05 (рис. 13.8). Установите генератор слов в пошаговый режим. Включите схему. С помощью соответствующих ключей установите состояние управляющих входов G1=1, G2A=G2B=0. Подавая слова от генератора слов, получите временные диаграммы работы дешифратора на экране логического анализатора и зарисуйте их в разделе "Результаты экспериментов". Сопоставьте временные диаграммы с таблицей 13.9.

Результаты экспериментов Эксперимент 1. Исследование работы дешифратора 3х8 в основном режиме. Таблица 13.1

С

Эксперимент 2. Исследование дешифратора 3х8 в режиме 2х4. a) Таблица 13.2

С

б)- Таблица 13.3

С

в) . Таблица 13.4

С

Эксперимент 3. Исследование работы дешифратора в качестве демультиплексора. Таблица 13.5

С

Эксперимент 4. Исследование дешифратора 3х8 с логической схемой на выходе. Таблица 13.6

G

1

Эксперимент 5. Исследование микросхемы 74138. а). Таблица 13.7

С

С

С

Вопросы

1. Какие логические функции выполняет дешифратор?

2. Каково назначение входов управления в дешифраторе, как влияет сигнал управления на выходные функции дешифратора?

3. Какие дополнительные логические элементы необходимы для реализации логических функции п аргументов на основе дешифратора с прямыми выходами? А с инверсными?

4. Как выглядит схема дешифратора 2х4, выполненная в базисе И, ИЛИ, НЕ? Входы дешифратора А, В, выходы YO, Yl, Y2, Y3. Сколько элементов каждого типа для этого требуется?

5. Как надо видоизменить схему дешифратора 2х4 в предыдущем случае, чтобы оснастить её прямым управляющим входом? Инверсным? Обозначьте входы дешифратора А, В, управляющий вход G или

7. Как на основе нескольких дешифраторов 2х4 с управляющим входом сделать дешифратор 4х16? Сколько дешифраторов 2х4 потребуется для решения этой задачи, если не использовать другие элементы?

8. Как на основе дешифратора 2х4 сделать схему, фиксирующую совпадение двух бит (А=В=1, А=В=0) и реализующую функцию

9. Как на основе дешифратора сделать логическую схему, реализующую функцию